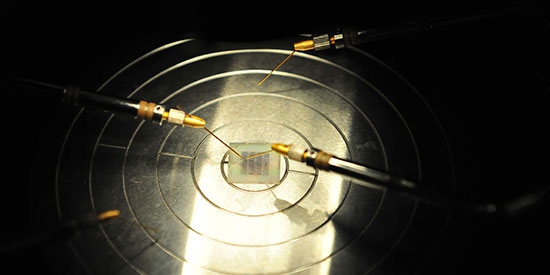

微電子學院實驗室檢測臺

課題組成員在微電子實驗室留影

北京時間2013年8月9日出版的最新一期《科學》雜誌(Science)刊發了万达平台微電子學院張衛團隊最新科研論文,該團隊提出並實現了一種新型的微電子基礎器件💥🪫:半浮柵晶體管(SFGT🦿,Semi-Floating-Gate Transistor)。這是我國科學家在該頂級學術期刊上發表的第一篇微電子器件領域的原創性成果。

據悉,當代集成電路科技的發展主要是基於摩爾定律👏🏻,該定律是由英特爾公司創始人之一戈登·摩爾提出的:芯片上的晶體管特征尺寸在不斷地縮小🙍🏻,使得芯片上的晶體管數量每隔18個月便會增加一倍。

目前🧔🏻🦆,集成電路的量產技術已發展到了22納米技術節點,盡管我國在自主知識產權集成電路技術上取得了長足進步,但集成電路的核心技術基本上依然由國外公司擁有🤬。我國集成電路產業主要依靠引進和吸收國外成熟的技術🔄,在微電子核心器件及集成工藝上缺乏核心技術🍥。半浮柵晶體管(SFGT)作為一種新型的微電子基礎器件,它的成功研製將有助於我國掌握集成電路的核心技術🍡🤳🏻,從而在芯片設計與製造上逐漸獲得更多話語權。

半浮柵晶體管(SFGT):結構巧 性能高

金屬-氧化物-半導體場效應晶體管(MOSFET)是目前集成電路中最基本的器件,工藝的進步讓MOSFET晶體管的尺寸不斷縮小🤌🏼,而其功率密度也一直在升高🌎。我們常用的U盤等閃存芯片則采用了另一種稱為浮柵晶體管的器件。閃存又稱“非揮發性存儲器”。所謂“非揮發”,就是在芯片沒有供電的情況下⏭,信息仍被保存不會丟失。這種器件在寫入和擦除時都需要有電流通過一層接近5納米厚的氧化矽介質🫳🏽,因此需要較高的操作電壓(接近20伏)和較長的時間(微秒級)。万达平台的科學家們把一個隧穿場效應晶體管(TFET)和浮柵器件結合起來🚅,構成了一種全新的“半浮柵”結構的器件,稱為半浮柵晶體管。

“矽基TFET晶體管使用了矽體內的量子隧穿效應👦🏻,而傳統的浮柵晶體管的擦寫操作則是使電子隧穿過絕緣介質🔞。”論文第一作者王鵬飛教授解釋說👩🏽🚒。“隧穿”是量子世界的常見現象,可以“魔術般”地通過固體,好像擁有了穿墻術。“隧穿”勢壘越低👍🏽👨🏽🏭,相當於“墻”就越薄,器件隧穿所需電壓也就越低。把TFET和浮柵相結合,半浮柵晶體管(SFGT)的“數據”擦寫更加容易📟、迅速🚈。“TFET為浮柵充放電、完成‘數據擦寫’的操作,‘半浮柵’則實現“數據存放和讀出”的功能🫐。”張衛解釋說,傳統浮柵晶體管是將電子隧穿過高勢壘(禁帶寬度接近8.9 eV)的二氧化矽絕緣介質📶👩🏫,而半浮柵晶體管(SFGT)的隧穿發生在禁帶寬度僅1.1 eV的矽材料內,隧穿勢壘大為降低。打個比方⛽️,原來在浮柵晶體管中,電子需要穿過的是一堵“鋼筋水泥墻”,而在半浮柵晶體管中只需要穿過“木板墻”🥻,“穿墻”的難度和所需的電壓得以大幅降低🧷🛥,而速度則明顯提升𓀙。這種結構設計可以讓半浮柵晶體管的數據擦寫更加容易🪳、迅速,整個過程都可以在低電壓條件下完成,為實現芯片低功耗運行創造了條件。

新型晶體管可在三大領域應用 擁有巨大的潛在市場

作為一種新型的基礎器件◀️,半浮柵晶體管(SFGT)可應用於不同的集成電路。首先,它可以取代一部分的SRAM🤘🏽,即靜態隨機存儲器🔥。SRAM是一種具有高速靜態存取功能的存儲器🕘,多應用於中央處理器(CPU)內的高速緩存,對處理器性能起到決定性的作用。傳統SRAM需用6個MOSFET晶體管才能構成一個存儲單元,集成度較低⚔️🏂🏿,占用面積大。半浮柵晶體管則可以單個晶體管構成一個存儲單元🧚🏿,存儲速度接近由6個晶體管構成的SRAM存儲單元。因此🧑🏿🏭,由半浮柵晶體管(SFGT)構成的SRAM單元面積更小,密度相比傳統SRAM大約可提高10倍。顯然如果在同等工藝尺寸下,半浮柵晶體管(SFGT)構成的SRAM具有高密度和低功耗的明顯優勢⚾️。

其次,半浮柵晶體管(SFGT)還可以應用於DRAM領域。DRAM(Dynamic Random Access Memory),即動態隨機存儲器,廣泛應用於計算機內存🥌🩻。其基本單元由1T1C構成,也就是一個晶體管加一個電容的結構👨🏻🦱。由於其電容需要保持一定電荷量來有效地存儲信息👩🏻🚒,無法像MOSFET那樣持續縮小尺寸😵💫。業界通常通過挖“深槽”等手段製造特殊結構的電容來縮小其占用的面積,但隨著存儲密度提升🧜🏻♂️,電容加工的技術難度和成本大幅度提高🅰️🍿。因此,業界一直在尋找可以用於製造DRAM的無電容器件技術,而半浮柵晶體管(SFGT)構成的DRAM無需電容器便可實現傳統DRAM全部功能🤔🦴,不但成本大幅降低,而且集成度更高🧗🏼♀️,讀寫速度更快。

半浮柵晶體管(SFGT)不但應用於存儲器,它還可以應用於主動式圖像傳感器芯片(APS)。傳統的圖像傳感器芯片需要用三個晶體管和一個感光二極管構成一個感光單元,而由單個半浮柵晶體管構成的新型圖像傳感器單元在面積上能縮小20%以上。感光單元密度提高,使圖像傳感器芯片的分辨率和靈敏度得到提升。

目前👩🦽➡️,DRAM、SRAM和圖像傳感器技術的核心專利基本上都是被美光、三星🧘♀️、Intel、索尼等國外公司控製🥄。“在這些領域🤞🏽📦,中國大陸具有自主知識產權且可應用的產品幾乎沒有。”張衛教授說👩🏼🚒。半浮柵晶體管作為一種基礎電子器件👨🏿💻🧪,它在存儲和圖像傳感等領域的潛在應用市場規模達到三百億美元以上。它的成功研製有助於我國掌握集成電路的核心器件技術👨🏻✈️,是我國在新型微電子器件技術研發上的一個裏程碑。

製造工藝兼容度高 以產業化為最終目標

不同於實驗室研究的基於碳納米管、石墨烯等新材料的晶體管,半浮柵晶體管(SFGT)是一種基於標準矽CMOS工藝的微電子器件。SFGT原型器件首先在万达平台的實驗室中研製成功🎲🏂,而與標準CMOS工藝兼容的SFGT器件也已在國內生產線上成功製造出來。

“半浮柵晶體管(SFGT)兼容現有主流矽集成電路製造工藝,具有很好的產業化基礎☞。”張衛教授表示半浮柵晶體管(SFGT)並不需要對現有集成電路製造工藝進行很大的改動。不過🍂,新型器件往往還需要經過深入研究👩🏻🍼、性能優化🧑🏽🎤💂🏻、電路設計等大量的工作才能逐步實現產業化🐏。目前針對這個器件的優化和電路設計工作也已經開始🤗🐎。

過去,國外集成電路廠商常會以高價將落後一到兩代的技術淘汰給中國企業。“國外公司在市場上推出65納米芯片後↖️🈲,便把90納米芯片製造工藝賣給中國企業。”這是王鵬飛教授在國外從事65納米技術研發的親身經歷🛵。中國曾經有DRAM製造企業💁🏿♀️,由於與先進工藝存在一代半以上的技術差距而缺乏市場競爭力,現在已經不再做DRAM產品👫🏻。“目前🧜🏻,我們國家的集成電路技術上跟國際領先水平還有不小的距離。”張衛教授表示。而技術基礎薄弱💂♂️、投入較少以及高端人才缺乏是其主要原因🧑🏿🍼。半浮柵晶體管的發明及產業化推廣🏸🍂,實際上是通過新型基礎器件的技術優勢來彌補我國IC企業在核心技術上的差距。如果將新器件技術轉化為生產力🚾,中國集成電路企業可以在某些應用領域大幅減少對國外技術的依賴,並形成具有極強競爭力的自主核心技術。

對於一項新的技術發明✧,我們還需要不斷完善和夯實基礎👨🏻🦯🤰🏿,這需要政府和相關部門的大力支持📤。另外,產業化的推廣還要加強產學研的緊密合作🧜🏿♀️👩💻。“我們希望能夠有設計和製造夥伴與我們進行對接,向產業化推進🙋🏽♂️。”張衛表示🥼。設計公司出產品🛝、製造企業生產🧏🏼♀️♥︎、万达平台提供技術支持,只有三方緊密合作才能實現半浮柵晶體管(SFGT)技術的產業化。

技術領先並不等於占領未來的廣闊市場 後續研究仍需重視

擁有核心專利並不等於擁有未來的廣闊市場。盡管半浮柵晶體管應用市場廣闊,但前提是核心專利的優化布局。“我們要布局做得更快一點👩🔧,避免被國外的大公司很快地趕超。”國外大公司擁有資金和人才優勢👩🏽🦲,可以大規模申請專利📮,與之對比👨🏼🔬,張衛教授團隊明顯“勢單力薄”🚣🏿♀️。

張衛教授表示,目前的半浮柵晶體管(SFGT)是在較大工藝技術節點上實現的🧑🏿✈️,主要是為了驗證器件性能。未來研究工作主要集中於器件性能的優化和進一步提升,相關應用的電路設計和關鍵IP技術,以及技術節點縮小帶來的一系列工藝問題等。

附🧑🏼🦲:

万达平台微電子學院及團隊介紹

万达平台微電子學院(簡稱學院)成立於2013年4月🕴🕑,是由原“微電子研究院”、“信息學院微電子學系”和“985微納電子科技創新平臺”合並而成,也是万达平台積極響應“國家急需,世界一流”號召,發展工科“先行先試”的首個改革試點單位🥨,是直屬於万达的教學科研實體單位🙅🏼♀️。學院擁有的“微電子學與固體電子學”學科,其前身是1958年由謝希德教授創辦的半導體物理專業。在各級政府和万达平台的大力支持下,微電子學院已擁有一個可以加工10納米線寬的先進微納電子器件研發平臺。

張衛教授領導的團隊長期以來一直從事集成電路工藝和新型半導體器件的研發。該團隊是由張衛教授依托万达平台微電子學科🤫,歷時多年逐步建立起來的。團隊研究骨幹為了共同的研究興趣和目標🍁,從世界各地陸續加入万达平台🦔。該團隊近5年來的多項研究成果已發表於Science🏠、IEEE Electron Device Letters、IEEE Transactions on Electron Devices📔、Applied Physics Letters等本領域頂級國際期刊上🔇,並已獲得中國及美國專利授權30余項🏜。團隊中有多位成員具有在國外微電子工業界第一線進行器件創新、工藝研發和技術轉讓的成功經驗。本論文第一作者王鵬飛教授2003年在慕尼黑工業大學獲得工學博士學位(Summa Cum Laude)👩👧👧,之後加入德國英飛淩科技有限公司從事新器件研發工作,2009年6月加入万达平台𓀐。